1999年4月第23卷第2期

#### 北方交通大学学报 JOURNAL OF NORTHERN JIAOTONG UNIVERSITY

Apr. 1999 Vol .23 No .2

# 高速数字印制电路板电源面/地面层结构 对 A I 噪声抑制的研究

## 任克宁 张林昌

(北方交通大学电子信息工程学院,北京100044)

摘 要 在高速数字印制电路板(PCB)上,在间距很小的电源面地面之间存在着一个层电容(一般为 0.02~200nF),该层电容对  $\Delta I$  噪声有抑制作用.本文采用混合位积分方程法(MPIE)和矩量法(MoM)建立了一个计算模型,从定量的角度分析和描述了在高频时(100 MHz~3 GHz) PCB 板的电源面/地面层结构对  $\Delta I$  噪声的作用.与实测数据相对比,该方法具有较高的精确度.并采用该方法定量地分析 PCB 板的电源面/地面层结构参数对  $\Delta I$  噪声的影响,据此提出了在高频时减小  $\Delta I$  噪声的具体方法.

关键词 高速数字印制电路板 ΔΙ噪声 混合位积分方程 矩量法

分类号 TN911.4 TN407

## Restriction on Delta I Noise Along the Power/ Ground Layer on the Highspeed Digital Printed Circuit Board

Ren Kening Zhang Linchang

$(\ College\ of\ Electronics\ and\ Information\ Engineering\ , Northern\ Jiaotong\ University\ , Beijing\ 1\,000\,44)$

Abstract On the hihgspeed digital printed circuit board (PCB), there exists a layer capacitance (generally from  $0.02\,\mathrm{nF}$  to  $200\,\mathrm{nF}$ ) between the closely spaced power and ground layers, which has some restriction on deltar I noise. According to MPIE (Mixed Potential Integral Equation) and MoM(Method of Moment), a model is developed to analyze and characterize quantitatively the restriction on deltar I noise by the power/ground structure on PCB in high frequencies (from  $100\,\mathrm{MHz}$  to  $3\,\mathrm{GHz}$ ). In comparison with the measured data from a testboard, the method produces relatively precise results. And several strategies are provided to reduce the deltar I noise in high frequencies.

**Key words** highspeed digital printed circuit board delta- I noise mixed potential integral equation method of moment

集成电路芯片在工作时会产生  $\Delta I$  噪声,该噪声将严重危及其他集成电路芯片的正常工作. 如何抑制  $\Delta I$  噪声日益成为电子电路设计中需要考虑的关键因素.根据  $\Delta I$  噪声产生的机理,可分为芯片级和电路板级两种.在一个集成电路芯片内,当一些驱动门电路发生"0" "1"转

化时,其上通过的电流发生突变.该突变电流沿电源线地线传导,对其他驱动门电路产生干扰,这就是芯片级  $\Delta I$  噪声干扰,目前已得到了比较全面的研究,尤其是在 CMOS 电路[1].在一个 PCB 板内,一些集成电路芯片在工作时产生  $\Delta I$  噪声,其沿着 PCB 板电源线地线结构传导,从而对另一些集成电路芯片产生干扰,这叫做电路板级  $\Delta I$  噪声干扰.如何抑制电路板级  $\Delta I$  噪声日益成为人们关注的焦点.

目前研究表明,在 PCB 板上安装去耦电容元件可以抑制  $\Delta I$  噪声.文献[2]表明:在低频时(f<100 MHz),去耦电容对  $\Delta I$  噪声有很强的抑制作用;但在高频时,因去耦电容的引线电感的存在,严重损害了去耦电容对  $\Delta I$  噪声的抑制作用.另外人们在研究中还发现,因在 PCB 板电源面和地面之间存在有层电容,对  $\Delta I$  噪声有抑制作用.在低频时其效果不明显,为去耦电容的作用所掩盖,在高频时效果明显.

本论文从定量的角度研究了当频率为  $100~\text{MHz} \sim 3~\text{GHz}$  时 PCB 板电源面/地面层结构对  $\Delta I$  噪声的抑制作用,采用混合位积分方程法 $^{[3]}(\text{MPIE})$  和矩量法 $^{[4]}(\text{MoM})$  计算 PCB 板上两个过孔之间的  $S_{21}$  散射参数,来衡量从一个过孔传导到另一个过孔的  $\Delta I$  噪声的大小,从而从理论上描述了 PCB 板电源面/地面结构对  $\Delta I$  噪声的抑制作用,并实际设计制造了一块试验板,采用惠普公司的网络分析仪 HP8510C进行了测试,并对实测数据与计算数据进行分析,得出了一些增强 PCB 板对  $\Delta I$  噪声抑制作用的方法和策略.

## 1 理论分析

$\Delta I$  噪声源就像分布在 PCB 板某处的一个振荡源,它产生了两种电磁波:一种是空间波 (Space Wave),一种是表面波(Surface Wave).空间波的能量集中于 PCB 板介质层中,只有少量向外辐射,表面波的能量则集中于 PCB 板金属面附近,它们均包含 TE 模和 TM 模.每一种模式的波都具有相应的谐振频率,由 PCB 板的结构参数决定.在这些频率处,PCB 板就像一个介质谐振腔,具有极高的 Q 值(为介质谐振腔的品质因素).从电磁兼容理论的角度来说, $\Delta I$  噪声是沿电源面和地面传播的传导发射(CE).当一个芯片运行时,其在与之相连的 PCB 过孔上引发电流的跳跃.这些电流的突变经过电源面和地面在另一个过孔上表现为电压的突变.当电压突变超过与该过孔相连的芯片正常工作所允许的范围时,将引发芯片的误操作,因此这两个过孔之间转移传输散射参数  $S_{21}$  成为衡量  $\Delta I$  噪声大小的根本参数.

#### 1.1 混合位积分方程法 (MPIE)

采用 MPIE 法是为了计算在外电场作用下金属体表面产生的分布电流密度,由此可计算得到需要的参数,如金属体表面的电压降及辐射的远场和近场分布.在具体数值计算时常采用 Mo M 法,这套方法在微带天线的参数计算中得到了广泛的应用[3].其 MPIE 方程为

$e_{\rm Z} \times E^{\rm E}(r) = e_{\rm Z} \times [{\rm j} \oint_s \overline{G_{\rm A}(r,r')} \cdot F_{\rm S}(r') {\rm d}s' + \nabla \int_s G_{\rm V}(r,r') Q_{\rm S}(r') {\rm d}s' + Z_{\rm S} J_{\rm S}(r)]$  (1) 其中, $E^{\rm E}(r)$ 为外在激励场, $J_{\rm S}(r)$ 和  $Q_{\rm S}(r')$ 分别为表面分布电流密度和表面分布电荷密度,它们符合电流连续性方程,r 和 r'分别为观察点和源点的坐标, $\overline{G_{\rm A}(r,r')}$ 和  $G_{\rm V}(r,r')$ 确定起来比较困难,精确地求得这两个 Green 函数的值实际是采用 MPIE 法进行计算的关键,对  $\overline{G_{\rm A}(r,r')}$ 和  $G_{\rm V}(r,r')$ 目前有多种计算方法,其中流行比较广泛的有 Mosig 提出的分段积分法[5]、离散复镜像法[6] 和本文采用的 Legendre 级数展开法[7].

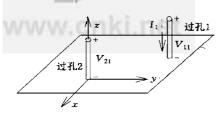

图 1 给出了典型的 PCB 板的电源面/地面的结构示意图. 图 1 中电流 I<sub>1</sub> 为沿过孔 1 的外

图 1 电源面/地面结构图

在单位激励电流  $_{I_1}$  权  $_{I_2}$  分别为由单位电流  $_{I_1}$  在 PCB 板过孔 1 和过孔 2 上产生的电压降 .同理 ,在过孔 2 存在单位激励电流  $_{I_2}$  ,它在过孔 2 和过孔 1 上分别产生电压降  $_{I_2}$  化  $_{I_2}$  (它们未在图 1 中给出) .由式(1)得到  $_{I_3}$  ( $_{I_3}$  )后 ,可以计算出电压  $_{I_1}$  、 $_{I_2}$  、 $_{I_3}$  、 $_{I_4}$  、 $_{I_5}$  和  $_{I_5}$  、 $_{I_5}$  为制度数  $_{I_5}$  为制度的传输特性 ,其值指示了干扰其他芯片  $_{I_5}$  从 噪声的大小 .由下式可以计算得到

$$S_{21} = \frac{2 V_{21}}{(V_{11} + 1) (V_{22} + 1) - V_{21} V_{12}}$$

(2)

#### 1.2 应用矩量法(MoM)实现数值计算

Mo M 法适于积分的数值计算,此法可对 MPIE 方程进行计算. 在计算中,整个 PCB 板分割成多个小区域,一般为长方形. 根据这种分割方式选定分域基函数和测试函数. 采用全域基函数往往需要对整个区域的表面分布电流密度进行估测,然后适当选取,如果估测不准将造成误差,所以本文不采用全域基函数. 在本文中表面分布电流密度  $J_{\rm S}(r)$  的分域基函数选定为Rooftop 函数. 根据电流连续性方式,表面分布电荷密度  $Q_{\rm S}(r')$  可以确定. 测试函数选定为矩形脉冲. 经过以上过程, $J_{\rm S}(r)$  和  $Q_{\rm S}(r')$  被离散化,以利于 Mo M 运算.

在计算中,外部激励电流 I 沿过孔流入和流出 PCB 板,并在过孔和板连接处均匀地放射性地展开.据此,本文设计了一种更简单的连接模式(Attach ment mode)来描述在此处电流和电荷的分布.当 PCB 板上表面分布电流确定以后,根据式(2)可以确定  $S_{21}$ .

## 2 实测及计算数据分析

目前,集成电路芯片一般为 TTL、CMOS 和 BiCMOS,其工作时波形边缘变化时间  $t_r$  一般为 1 ns 左右,由数字信号基频估算公式  $f_1=0.35/t_r$ ,可知其信号频谱之基频约为 350 MHz.信号中高次谐波成分逐渐减小,考虑到信号的 7 次谐波,则其频谱范围约为 2.4 GHz.因为集成电路芯片工作时产生  $\Delta I$  噪声的频谱范围与其数字信号的频谱范围大致相等,因有一些冗余,本文确定研究的  $\Delta I$  噪声的频率范围为 3 GHz.

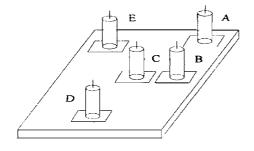

实测时,设计了一个测试板,两面为金属面.板上焊接了 5 个 S MA 型接头,用于测试时与网络分析仪 HP8510C 连接.其结构如图 2 所示, A B 、C、D 和 E 为 5 个 S MA 接头.测试板的参数为:①尺寸( $a \times b \times h$ ):长 70 mm、宽 70 mm、厚 1 mm.②金属面:铜,电导率为 5.8×10<sup>7</sup> S/m,厚度为 0.001 8 mm.③介质层:TP-1,相对介电常数  $\varepsilon$  = 2.8,损耗角正切值为 0.001.

图 2 测试板结构图

表 1 在 100 MHz ~ 3 GHz 范围内 PCB 板之谐振频率

| 谐振模式                            | f / GHz |

|---------------------------------|---------|

| T $M_{01}$ , T $M_{10}$         | 1 .276  |

| T M <sub>11</sub>               | 1 .805  |

| T $\rm M_{02}$ , T $\rm M_{20}$ | 2 .553  |

| T $M_{21}$ , T $M_{12}$         | 2.854   |

经计算,该 PCB 板电源面与地面之间的层电容  $C_0$  为 0.121 3 nF,其  $S_{21}$  参数如图 3 所示.设自由空间波数用  $k_0$  表示,由于测试板参数符合  $k_0$  h  $\sqrt{\varepsilon}$  - 1 <  $\pi/2^{[5]}$  ,所以在板上不存在 TE 模表面波,只有 TM 模表面波.在不考虑 SMA 接头位置,把 PCB 板近似为一个介质振荡器计算出一阶,二阶 TM 模式的谐振频率.其谐振频率如表 1 所示.

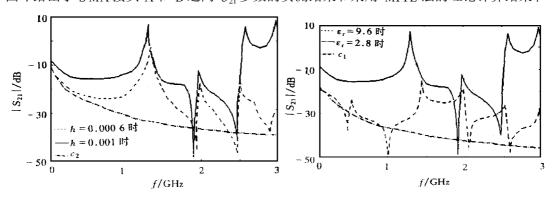

在 PCB 裸板 (未安装去耦电容) ,对  $\Delta I$  噪声的抑制只能靠层电容来实现 .图 3 给出了使用网络分析仪 (HP8510C) 对测试板的实测结果 ,并与只有层电容  $C_0$ 、未安装去耦电容裸板的理论计算结果相对比 .

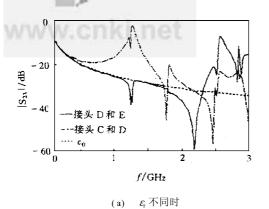

从图 3 中可以发现,在 f<500 MHz 时,在测试板上不同位置(SMA接头)实测的  $S_{21}$ 与层电容  $C_0$  的理论计算参数非常近似.这说明,在此频段 PCB 板对  $\Delta I$  噪声的抑制作用不受位置的影响,并且此时对  $\Delta I$  噪声的抑制完全由层电容来实现.在  $f\leqslant 1.8$  GHz 时,PCB 板 TM 模谐振频率不受 SMA接头的具体位置影响,当 f>1.8 GHz 后,PCB 板 TM 模谐振频率受到接头位置的影响,此时将 PCB 近似为介质的振荡器,不能得到谐振频率的精确结果.在 f>500 MHz 时,实测的数据曲线发生振荡并偏离层电容  $C_0$  的理论计算结果.究其原因,这是由于PCB 板形如一个介质谐振器在某些频率处发生谐振,及 PCB 板的边缘发生电磁波辐射和反射(边缘效应)的结果,再加上其它一些偶然因素的影响,如 PCB 板的结构参数、SMA接头的质量和与测试板焊接的好坏,所以可依靠设定 PCB 板的参数来控制板子对  $\Delta I$  噪声的制约效果.图 4 给出了 SMA接头 A和 D之间  $S_{21}$ 参数的实测结果和采用 MPIE 法的理论计算结果.

图 3 测量所得的接头之间  $S_{21}$  的 模值与裸板的计算结果

图 4  $A D 之间 S_{21}$  的理论计算和实测数据比较

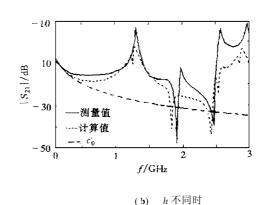

图 5 为在不同情况下接头 A和 D之间  $S_{21}$ 参数的理论计算结果 .图 5 中 ,当  $\varepsilon_r$  = 9 .6 、h = 0 .001 m 时 PCB 板的层电容  $C_1$  为 0 .415 9 nF .当  $\varepsilon_r$  = 2 .8 、h = 0 .000 6 m 时 PCB 板的层电容  $C_2$  为 0 .202 2 nF .观察图 4 和图 5 可以发现 : ①采用 MPIE 法的计算数据与使用网络分析仪的测试结果变化趋势非常接近 ,说明本文根据 MPIE 和 MoM 法建立的计算模型比较精确地反映了 PCB 板上  $S_{21}$  的变化规律 ,可用来预测 PCB 板电源面/地面结构对  $\Delta I$  噪声的抑制作用 .② $\varepsilon_r$  = 9 .6 时的  $S_{21}$  幅度值比  $\varepsilon_r$  = 2 .8 时下降了约 10 dB ,但是在更多的频率点上发生谐振 .可认为 ,增加 PCB 板的  $\varepsilon_r$  值不失为一个非常有效的策略 . 但由于谐振点增多 ,增加了  $S_{21}$  参数随频率变化的复杂性 ,对于较高频率下抑制  $\Delta I$  噪声的效果不易控制 .③PCB 板 b = 0 .6 mm 时的  $S_{21}$  幅度值比 b = 1 mm 时下降了约 5 dB. 所以减小 PCB 板的 b 值也是一个降低  $\Delta I$  噪声的有效方法

图 5 在不同情况下  $A \setminus D$  之间  $S_{21}$  的理论计算

## 3 结论

PCB 板上电源面和地面之间安装去耦电容后,在低频(f<100 MHz)时,该去耦电容对  $\Delta I$  噪声有极大的抑制作用,但在高频,其抑制效果被去耦电容的引线电感破坏殆尽.在 PCB 板未安装去耦电容时,当频率从100 MHz 到500 MHz 时,PCB 板电源面与地面之间的层电容 对  $\Delta I$  噪声有较大的抑制作用,但频率进一步提高后,其效果被电磁波的谐振、PCB 板的边缘 效应以及其它一些 PCB 板结构上的偶然因素所破坏,因此应该采用一些策略来控制层电容对 更高频率段的作用.

本文利用 MPIE 和 Mo M 法建立了一个计算机模型,来计算频率在 100 MHz 到 3 GHz 时的  $S_{21}$  散射参数幅度值.该型给出了比较精确的结果,可以用来进一步分析 PCB 板上  $\Delta I$  噪声的变化规律.在对一个测试板的实测结果和理论计算结果进行了分析之后,可以得出以下一些有效抑制  $\Delta I$  噪声的策略:①设计 PCB 板时,采用具有较高相对介电常数的介质作基片.②在不影响生产成本的前提下.尽可能减小介质层的厚度.并采用多对电源面/地面结构.

另外,本文还提出以下建议:在设计使用多对电源面/地面结构时,为减少  $\Delta I$  噪声源和  $\Delta I$  噪声的受害者,尽量减少每对电源面/地面上所接集成电路芯片.在 PCB 板上,尽量少设计过孔和金属化孔,以减少  $\Delta I$  噪声源的干扰途径.

#### 参考文献

- 1 Senthinathan R, Prince J.Simultaneous Switching Noise of CMOS Devives and Systems. Boston: Kluwer, 1994.99 ~ 115

- 2 Shi H, Sha F, Drewniak J, Van Doren, Hubing T. An Experimental Procedure for Charcteriaing Inteconnects to the DC Power Bus on a Mustilayer Pirinted Circuit Board. IEEE Trans. EMC, 1997, 39(4):279 ~ 285

- 3 Mosig J R, Gardiol F E. General Integral Equation Formulation for Microstrip Antennas and Scatters. IEE Proc. H, 1985, 132  $(7):424 \sim 432$

- 4 Harrington R F . Field Computation by Moment Methods . New York : Mc Millan ,1968 .1  $\,\sim\,\,22$

- 5 James J R, Hall PS. Handbook of Microstrip Antennas .Stevenage: Peter Peregrinus, 1989.393 ~ 453

- 6 王健,王石安.离散复镜象理论对近地电偶极子的应用.电子科技大学学报,1990,19(6):564~571

- 7 Laheurte J M, Rousta M, Marchetti S.Improved Frequency Domain Analysis of Microstrip Circuits by the Method of Moments. IEE Proc. H, 1995, 104(6):421 ~ 428